返回

列表

列表

SPI协议优缺陷 怎么削减GPIO数量

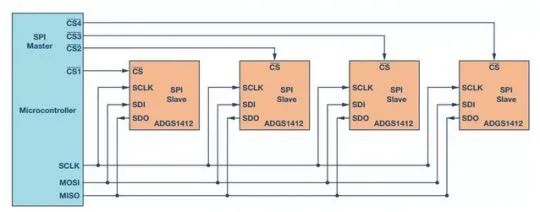

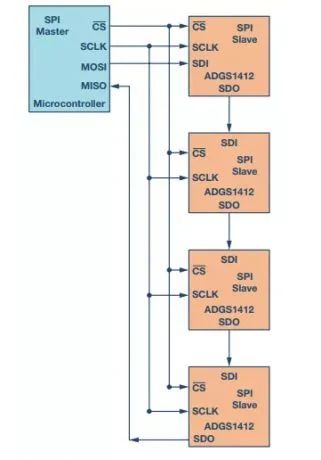

发表时间: 2024-01-23 作者: 常见问答另一种办法是运用SPI操控的开关。此办法的长处是可削减所需GPIO的数量,而且还能消除外加串行转并行转换器的开支。如图所示,不需要16个GS1412供给SPI信号。开关可选用菊花链装备,以逐渐优化GPIO数量。在菊花链装备中,不管体系运用多少开关,都只运用主机(微操控器)的四个GPIO。

图用于阐明意图。ADGS1412数据手册主张在SDO引脚上运用一个上拉电阻。为简略起见,此示例运用了四个开关。跟着体系中开关数量的添加,电路板简略和节约空间的长处很重要。

在6层电路板上放置8个四通道SPST开关,选用4×8交叉点装备时,支撑 SPI 的开关可节约20%的总电路板空间。

SPI 的长处是它有着比I2C更高的吞吐量,不被最大时钟速度所约束,可完成潜在的高速、极为简略的硬件接口,外围电路运用的上拉电阻是比 I2C

协议更少的,这在某种程度上预示着它具有比I2C的功耗更低、从机的时钟来历来自主机设备,无需新增精细振荡器、从机不需要仅有的地址、相对于并行接口而言,运用的引脚数目大幅度削减等长处。

但一起有着必定的缺陷,例如SPI没有带内寻址、当运用多个不同形式的从机设备时,主机设备切换形式时从头初始化,会使得拜访从机设备速度变慢、SPI从机设备没有硬件流控,只可以经过主机自主的推迟下个时钟周期到来的时刻、仅能在短距离通讯等缺陷。但能在防止SPI的缺陷的方历来使用SPI的话,SPI的长处让它远远优于其他协议。